- 信号链是连接真实世界和数字世界的桥梁。随着ADC采样率和采样精度的提升,接口芯片的信号传输速度也越来越快,高速信号传输的各种挑战慢慢浮现出来了。作为一个信号链设计或验证工程师,这些基本概念你一定要知道。相比传统的CMOS传输技术,在信号链中引入LVDS或JESD204B,可以实现更高的信号传输速率,更低的功耗,具备更好的抗干扰性 (信噪比更佳),而且线束数量会大幅降低。LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Se

- 关键字:

信号链 高速信号 LVDS JESD204B

- Microchip的PolarFireR FPGA产品业界认证具有出色可靠的低功率、高安全性组件,一直被广泛应用于有线和无线通信、国防、航空、工业嵌入式、人工智能、图像处理等不同范畴。本文将介绍如何在PolarFire Splash套件上实现JESD204B独立设计,并搭配GUI演示应用的电路板。此设计是使用PolarFire高速构建的参考设计收发器模块,以及CoreJESD204BTX和CoreJESD204BRX IP内核。它在运行时透过收发器将CoreJESD204BTX数据发送到CoreJESD2

- 关键字:

PolarFire FPGA Splash套件 JESD204B 串行接口

- FMC+标准将嵌入式设计推到全新的高度- 作为使用 FPGA 和高速 I/O 的嵌入式计算设计的重要发展,名为 FMC+ 的最新夹层卡标准将把卡中的千兆位收发器(GT)的总数量从 10 个扩展到 32 个,最大数据速率从 10Gbps 提升到 28Gbps,同时保持与当前 FMC 标准实现向后兼容。

- 关键字:

嵌入式 JESD204B 连接器

- JESD204B接口是一个串行解串器链路规范,允许12.5Gbps的最大数据速率传输。使用高级工艺(例如65nm或更小)的转换器支持该最大数据速率,还可提高电源效率。系统设计人员可充分利用该技术相对于低压差分信号(LVDS)DDR的优点

- 关键字:

数据转换器 JESD204B LVDS PHY模式

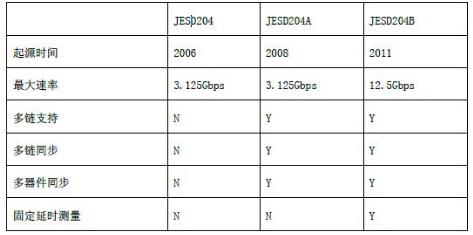

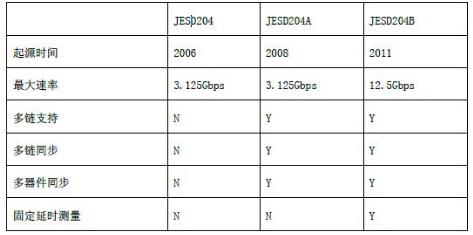

- 目前,将JESD204B作为高速数据转换器首选数字接口的趋势如火如荼。JESD204接口于2006年首次发布,2008年改版为JESD204A,2011年8月再改版为目前的JESD204B。与LVDS等以前的技术相比,该接口在效率上技高一筹,同时还

- 关键字:

JESD204B 链路 数据转换

- 对于需要一系列同步模数转换器(ADC)的高速信号采样和处理应用,转换器具有去相位偏移和匹配延迟变化的能力至关重要。围绕该特性展开的系统设计极为关键,因为从模拟采样点到处理模块之间的任何延迟失配都会使性能下

- 关键字:

JESD204B ADC FPGA

- 针对某宽带雷达数字接收机对带宽、动态、处理速度、多通道等指标的需求,设计了一种基于新型ADC器件AD9680的宽带高动态全数字雷达接收机验证平台。文中首先在搭建的平台上对AD9680进行全带宽模式和数字下变频模式的性能验证与结果分析,根据分析结果提出改善AD9680动态性能的方案;其次,对AD9680两个通道之间的同步性做了验证,并提出了一种针对双通道时间偏差的优化方法。各项结果表明,AD9680能满足某宽带雷达的应用需求。

- 关键字:

AD9680 宽带雷达数字接收机 JESD204B 数字下变频 双通道同步

- 摘要 在通信设施、成像设备、工业仪器仪表等需要大量数据的系统中,要求数据转换级提供越来越宽的分辨率和越来越高的采样率。并行接口的物理布局和串行LVDS方法的比特率限制,给设计人员带来技术障碍。文中基于Xili

- 关键字:

GTX Xilinx VertX6 JESD204B

- Analog Devices, Inc.,全球领先的高性能信号处理解决方案供应商,最近推出一款高性能时钟抖动衰减器HMC7044,其支持JESD204B串行接口标准,适用于连接基站设计中的高速数据转换器和现场可编程门阵列(FPGA)。JESD204B接口专门针对高数据速率系统设计需求而开发,3.2 GHz HMC7044时钟抖动衰减器内置可以支持和增强该接口标准特性的独特功能。HMC7044提供50 fs抖动性能,可改善高速数据转换器的信噪比和动态范围。该器件提供14路低噪声且可配置的输出,可以灵活地

- 关键字:

Analog Devices JESD204B

- 1 为不同应用提供不同选择

对于数据转换器的高速串行传输,不同的应用有不同的选择。十多年来,数据转换器制造商一直选择LVDS作为主要差分信号技术。尽管有些LVDS应用可使用更高的数据速率,但目前该市场上的转换器厂商可提供的最大LVDS数据速率仍然为0.8至1 Gbps。LVDS技术一直难以满足转换器的带宽要求。LVDS受TIA/EIA 644A规范控制,这是一项LVDS核心制造商的行业标准。该规范可作为设计人员的最佳实践指南,提高不同厂商的LVDS发送器及接收器兼容性。同样,没有完全遵守LVDS

- 关键字:

JESD204B LVDS 转换器 FPGA PHY

- 在要求高速数据生成和采集的市场中,性能是关键。为了让模数转换器 (ADC)、数模转换器 (DAC) 以及模拟前端 (AFE) 实现更简易的直接连接,德州仪器 (TI) 日前宣布推出基于KeyStoneTM的高集成度66AK2L06片上系统 (SoC) 解决方案,为行业带来更多选择。66AK2L06 SoC集成了JESD204B接口标准,让总体电路板封装尺寸实现了高达66%的缩减。该集成也可帮助航空电子、防御系统、医疗以及测试与测量等市场领域的用户开发出具有更高性能同时能耗减少高达50% 的产品。此外,

- 关键字:

德州仪器 JESD204B

- 随着数模转换器的转换速率越来越高,JESD204B串行接口已经越来越多地广泛用在数模转换器上,其对器件时钟和同步时钟之间的时序关系有着严格需求。本文就重点讲解了JESD204B数模转换器的时钟规范,以及利用TI公司的芯片实现其时序要求。

1. JESD204B介绍

1.1 JESD204B规范及其优势

JESD204是基于SerDes($174.9800)的串行接口标准,主要用于数模转换器和逻辑器件之间的数据传输,其最早的版本是JESD204A,现在是JESD204Bsubclass

- 关键字:

JESD204B 数模转换器

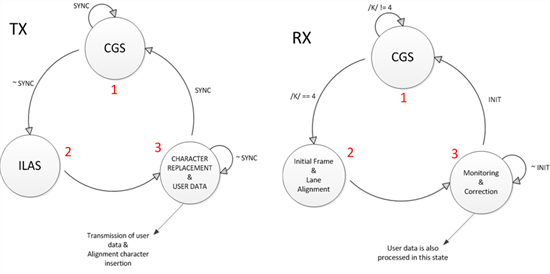

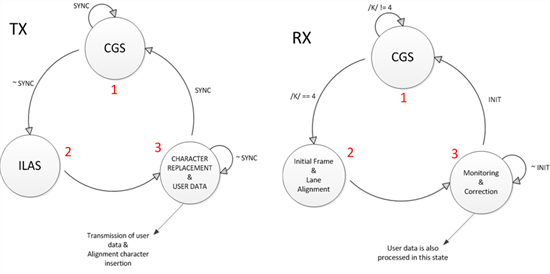

- 在使用我们的最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。此外,我还在 E2E 上的该栏目下阅读了各种技术文章及其它博客文章,明白了为什么 JESD204B 是 LVDS 和 CMOS 接口的后续产品。

有一个没有深入讨论的主题就是解决 ADC 至 FPGA 和 FPGA 至 DAC 链路问题的协议部分,这两种链路本来就是相同的 TX 至 RX 系统。作为一名应用工程师,我所需要的就是

- 关键字:

JESD204B FPGA DAC

- 2014年1月24号,Altera公司(Nasdaq: ALTR)宣布,开始提供多种JESD204B解决方案,设计用于在使用了最新JEDEC JESD204B标准的系统中简化Altera FPGA和高速数据转换器的集成。很多应用都使用了这一接口标准,包括雷达、无线射频前端、医疗成像设备、软件无线电,以及工业应用等。

- 关键字:

Altera JESD204B 转换器 FPGA

- 拥有模拟和数字领域的优势技术、提供领先的混合信号半导体解决方案的供应商 IDT®公司 (Integrated Device Technology, Inc.; NASDAQ: IDTI) 日前发布业界首款低功率双通道 16 位、具备 JESD204B 的数模转换器(DAC),该器件适用于多载波宽带无线应用。

- 关键字:

IDT DAC JESD204B

jesd204b介绍

您好,目前还没有人创建词条jesd204b!

欢迎您创建该词条,阐述对jesd204b的理解,并与今后在此搜索jesd204b的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473